发布日期:2022-04-18 点击率:28

三星公司已经开始量产其48层(即单NAND内48层单元,属于第三代升级技术)3D V-NAND芯片,预计其将被用于SSD T3(mSATA接口加850 EVO V2)、NVMe SSD(PM971-NVMe)以及企业级SSD(PM1633a)等SSD产品。在各设备当中,将包含大量48层3D V-NAND存储芯片且通过引线键合技术实现彼此堆叠。三星公司在48层3D V-NAND芯片中集成了512 GB存储单元,意味着每个NAND晶片为32 GB容量(256 Gb)。三星的32层(第二代方案)3D V-NAND晶片则为10.67 GB容量(85.33 Gb)。因此,第二代与第三代3D V-NAND设备之间到底存在哪些差别?是否单纯只是将单元层数由32提升到48?

对此,我们对两款设备进行深入剖析,着眼于单元架构、材质、布局以及封装等角度。下面来看分析结论:

存储密度与晶片平面图

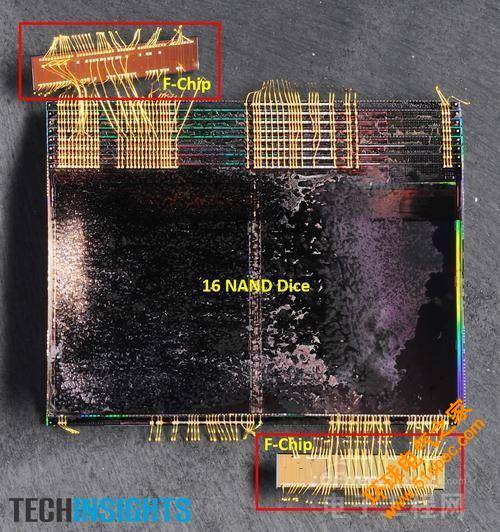

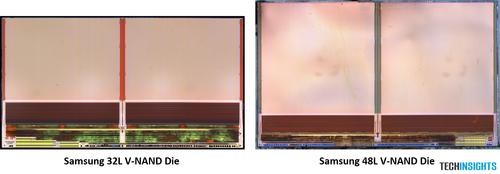

图一所示为16 48层3D V-NAND晶片,MCP(即多芯片封装)内包含双F-Chips。48层的裸片效率显然更高。32层3D V-NAND晶片面积为84.3平方毫米,而48层3D V-NAND晶片则为99.8平方毫米,意味着其长度较上代方案提升17.3%(如图二所示)。每单元晶片存储密度则提升至2.57 Gb每平方毫米。而目前最顶级的高密度2D平面NAND设备为东芝的15纳米TLC NAND,具体水平为1.28 Gb每平方毫米。二者之间的最大差异在于:1)平面(NAND存储阵列)区,2)位线开关与页缓冲区,3)逻辑与外围区以及4)加入F-Chips。每块晶片分为两层。NAND存储阵列区由原本的48.9平方毫米增加至68.7平方毫米,提升为40.3%。而位线开关电路则与32层方案保持一致,不过页面缓冲区则缩小了20%。逻辑与外围电路面积减少34.8%。换言之,三星方面大幅削减了页缓冲与周边区面积,从而使其在存储密度与晶片效率方面得到提升。另外,16层堆叠设计中的晶片厚度也由132微米降低至36微米。

图一,三星48层3D V-NAND设备,采用16层垂直堆叠NAND晶片与双F-Chips,拆机图片。

图二,32层与48层3D V-NAND对比。

F-Chip闪亮登场

三星公司在去年的ISSCC2015大会上首公宣布将F-Chip嵌入至其NAND闪存封装当中。总体来讲,SSD硬件架构是由存储控制器、NAND闪存与DRAM所共同构成。

F-Chip负责在存储控制器之间的I/O总线上实现点对点拓扑,另外F-Chip还会对通道内的不必要反射进行缓冲。另外,F-Chip在其与NAND设备之间建立了两套内部I/O总线,从而降低F-Chip到NAND接口的容量负载。另外,其支持再定时模式,旨在从存储控制器中将I/O信号传输至NAND设备。

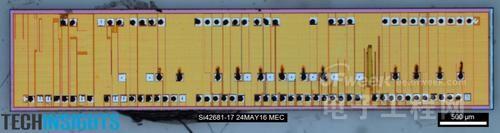

再有,F-Chip亦改善了NAND设备与异步接口中出现的时序容限所引发的定时不稳状况。单一F-Chip接入八块V-NAND晶片,意味着双F-Chips可嵌入至16晶片封装内。图三所示为从MCP中分离出来的F-Chip,其中包含ROM、DC发电、CMD译码器、数据路径、TX/RX以及引线接合盘等电路元件。F-Chip晶片面积为0.057平方毫米。

图三,从三星48层3D V-NAND MCP中拆分出来的F-Chip晶片

下一篇: PLC、DCS、FCS三大控

上一篇: 索尔维全系列Solef?PV