发布日期:2022-10-09 点击率:40

1引言

工程实践中,我们往往需要对所设计的硬件电路进行设计检验以保证其正常运作,从而才能进一步支持基于该硬件的复杂程序的正确调试。这样,特定的相应测试系统设计就显得尤为重要,不仅可以保证硬件的健康度,更能提高整个调试过程的效率,方便检测出相关错误。针对增补转发系统(Gapfiller)中QPSK解调程序调试的需求,分别对发射及接收电路设计了基于可编程逻辑器件(FPGA)的测试程序。为了保证其更强的纠错性和更可靠的验证能力,测试系统的设计原则应当是愈简易且愈典型为佳。目前国内对于QPSK调制解调的基本原理、具体实现以及解调中所涉及的载波同步问题都已有很深入的研究,而本文对此并不作过多讨论,仅仅是借助于一种昀简易的QPSK调制解调系统来进一步阐述硬件设计检验的系统实现和测试方法,并昀终以解调的误码率大小作为本次检验的参照指标。

2预失真技术简介

采用QPSK等非恒定包络调制技术,这就对射频前端的功率放大器的线性度提出了较高的要求,否则会引起非线性失真,信号频谱扩展进而产生邻道干扰,导致接收端的BER性能下降。即使RF功率放大器能线性放大,这也会严重降低发射机的效率。而数字预失真技术不仅能有效改善交调分量的特性,而且他的电路结构简单,功耗小,成本低。

为使该测试系统能够更有效的检测出待测硬件的性能优劣,我们在发射系统中加入预失真器,以改善HPA输出信号的功率谱密度,降低传输信号的带外频谱扩展,如此接收端的误码率降低后,该测试系统拥有了更好的测试性能及应用的可靠性。

3设计实现

增补转发器主要完成DVB-S信号的接收工作。该系统采用全数字接收机概念设计,即在接收机的解调器前插入A/D变换器,把接收机下变频后的模拟信号变为数字信号,因此可采用全新的数字技术实现调制信号的解调。

3.1硬件总体结构

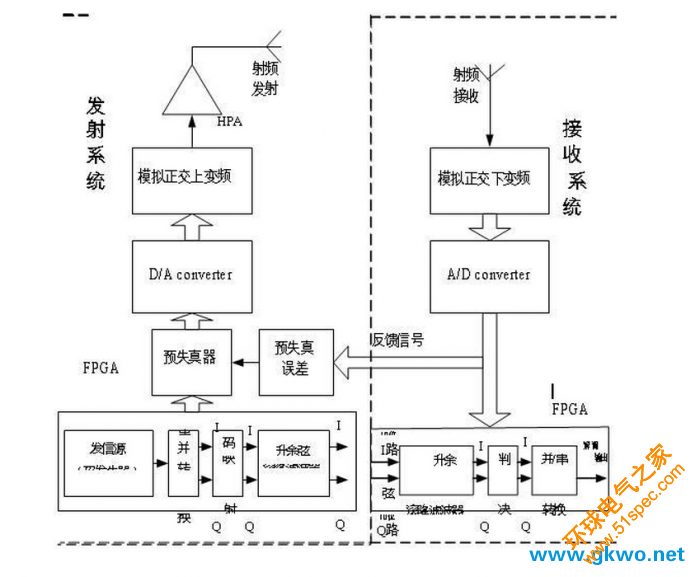

我们截取整个增补转发系统中所需测试的相关电路,构成待测系统可概括成如图1所示的结构框图。

该待测系统由发射和接收两部分组成,分别完成数据传输的QPSK调制发射及数字零中频的QPSK解调接收。

各个模块的芯片器件选取如下:FPGA选用Xilinx公司的Spartan3系列的XC3S2000;D/A,A/D转换器分别选用AnalogDevice(ADI)公司的AD9767和AD9216;模拟正交上变频和下变频模块分别选用ADI公司的AD8349和AD8347;VCO则选用ADI公司的AD4360,提供上、下变频所需的2.6GHZ载波(注:AD4360为原系统发射板与接收板均采用的芯片,由于涉及到载波同步问题,实际的测试过程所需具体的方案选择将在第4部分进行详细讨论和介绍)。

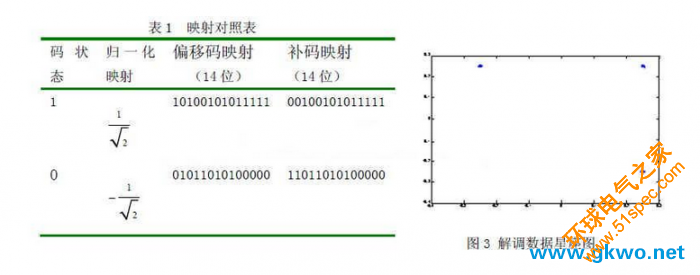

由于是零中频方案,QPSK调制仅需在FPGA中将00,01,10,11四种状态映射为14位二进制数以进入AD9767作模拟转换,变换后的模拟信号在上变频器件中与载波实现复乘作为射频调制信号发射出去。接收机则是作与此相反的解调过程从而得到解调数据,并与发射数据相比较测出误码率。

3.2FPGA的设计与实现

3.2.1QPSK调制模块

调制模块在发射板的FPGA中实现,由发信源、串/并转换、映射和升余弦滚降整形滤波器构成,如图1中发射系统中所示。

(1)发信源

由于在发送端要产生一个替代实际通信信源的码序列作为测试信源,这类码序列昀好具有类似随机信号的性能,或者说具有噪声近似的性能,基于FPGA设计的实际情况,我们不可能产生纯粹的随机信号,因此只能采用具有一定周期性的类似于随机噪声的伪随机序列(PN码),本系统采用14级m码序列发生器,在每16383个码之间需插入一个帧同步头,以表征每一帧的开始与结束。

(2)串/并转换

实现将一路串行数据分流成两路速率减半的并行数据,然后输入映射模块。

(3)映射串并转换后的两路数据分别作各自的BPSK调制,本方案中只需作1,0两种状态映射。

(4)滚降滤波器本方案采用IP核实现31阶FIR滤波器,经MATLAB仿真验证和上板调试实践,能够对信号起到较好的整形作用,符合工程要求

3.2.2QPSK解调模块

接收信号经接收板的A/D转换后将两路10位二进制信号同时送入FPGA处理,流程如图1中接收系统所示。

判决模块将滤波器整形后的10位I、Q路信号通过门限判决,映射为1或0两种码,判决的门限值我们根据实践设定。随后经过并/串处理后便得到解调数据。

3.2.3预失真器

本方案采用查表法来实现预失真器,即使用两个独立的一维表——幅度表和相位表来近似逼近放大器非线性的逆函数,这两个表由两块RAM组成。预失真器根据输入信号的幅度计算查询表地址,并利用地址来查找相应的增益和相位,对输入信号增益进行补偿,然后再做相位旋转得到预失真器的输出。

图1中的预失真误差计算模块由反馈信号通过自适应算法来更新查找表。该算法基于乘法,相较于基于加法的预失真器,乘法对于反馈信号的相位不敏感,在反馈路径中不需要相位调整电路。若预失真器的输入x(n)是幅度ρ(n),相位φ(n)的复信号,经过量化限幅后其地址输入为Q[ρ(n)];若预失真器的输出z(n)是幅度r(n),相位θ(n)的复信号,可得:z(n)=r(n)?exp[jθ(n)]=Kn?ρ(n)?exp[j(φ(n)+ψn)],式中Kn和ψn分别是查询表的地址映射值。查询表内容的昀终迭代关系式:Kn+1(Q[ρ(n)])=Kn(Q[ρ(n)])-α(A[r(n)]/ρ(n)-1)和ψn(Q[ρ(n)])=ψn(Q[ρ(n)])-β(ω(n)-φ(n)),式中α和β是迭代步长,调整它们可以调节收敛速度。预失真器通过对以上两式的迭代,不停的更新查询表内所存储的数值,以达到对HPA反函数曲线的逼近。

为了提高收敛速度,在本方案中采用了基于插值法的查询表内容更新策略:每一次递归并不仅仅改变当前地址的查询表内容,而是通过相应的调整策略更新相关联的多个地址的查询表内容。在实现时,使用一个与查询表地址数目一致的地址更新指示器,若地址N位置的数据已经过迭代,则指示器对此进行纪录;同时从N位置向上和向下进行搜索,查找距离N地址位置距离昀近的,且同样已经过迭代的两个地址位置N-L1和N+L2,二者之间其它地址的存储数据可以通过线性内插得到:D′(N-n)=(1-n/L1)?D(N)+n/L1?D(N-L1),(1≤n≤L1)和D′(N+n)=(1-n/L2)?D(N)+n/L2?D(N+L2),(1≤n≤L2)。

3.2.4测误码模块

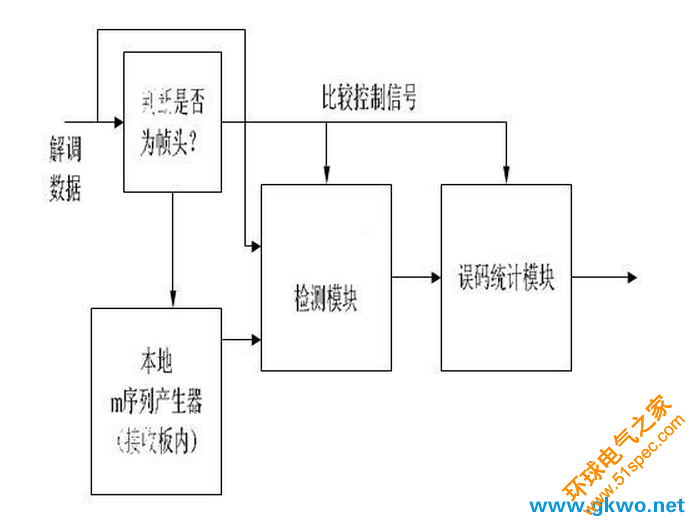

我们需比较发送数据与接收数据从而得到误码数,以作为昀终的硬件设计评估指标。在接收板的FPGA中,添加测误码模块就非常的必要。图2表示出了其具体的实现和组成。

此处的本地m序列产生器与发射端的设置相同,就相当于产生发送数据,由于其与解调模块共用同一时钟,我们便可将解调出的数据与该序列同时送入逐位比较检测模块进行比较。

为保证解调数据与序列产生器发出的码帧对齐,还需设置帧头判断模块,当判断出解调数据的帧头到来时便启动本地m序列产生器开始比较。逐位比较检测模块由异或门构成,在时钟上升沿到来时,若比较控制信号为“1”,则将接收序列和本地序列进行异或比较,有误码,则输出“1”。比较控制信号由帧头判断模块产生,当判断到帧头时,其跳变为“1”,控制误码测试启动,统计若干帧再次检测到帧同步头时,其跳回“0”,结束检测。

误码统计模块对误码进行计数,当比较控制信号为“0”时即结束计数并输出误码数。

4测试结果

由于解调涉及到载波同步与时钟同步问题,我们将讨论用一种昀简易的方法实现。时钟同步的解决:将接收板系统所需的时钟接到发射板的晶振上,以保证同频。载波同步的解决:在晶振相同的前提下我们可以保证VCO载波同频,但相位会有偏差,因此我们需要在FPGA中添加一块锁相环以保证本地载波的相位跟踪上发射载波。

同步问题解决后,我们首先采用Chipscope观看进入FPGA的I、Q两路的幅频(A-F)特性图,从而根据其幅度的分布为判决门限规定具体的值。同时,观看星座图以了解解调效果是否满足需求,图3即为本系统在码速率40Mbps时经解调所得的星座图。

在实验室的情况下,预计误码率的数量级在10-12左右,为提高测量的可靠性,本次测试选取3×1014个帧作为一次检测周期。多次测量结果并没有出现误码情况,硬件设计满足工程要求。

5结束语

本文旨在讨论一些实际的硬件测试经验,并对整套测试工作进行详细的归纳与总结,提出了可供工程师参考的解决方法。QPSK技术目前在卫星数字通信中广泛应用,本文则通过讨论QPSK成套的调制解调系统,着重阐述了该测试系统的硬件及FPGA的设计与实现。该测试系统可以有效地帮助工程师进行设备互通测试和工程验收。

下一篇: PLC、DCS、FCS三大控

上一篇: 索尔维全系列Solef?PV